Há muito tempo eu li o CODE e fiquei bem impressionado. É uma ótima viagem por todas as camadas de abstração de um computador. O autor começa com elementos muito simples e nos traz cada vez mais perto de entender como um computador funciona.

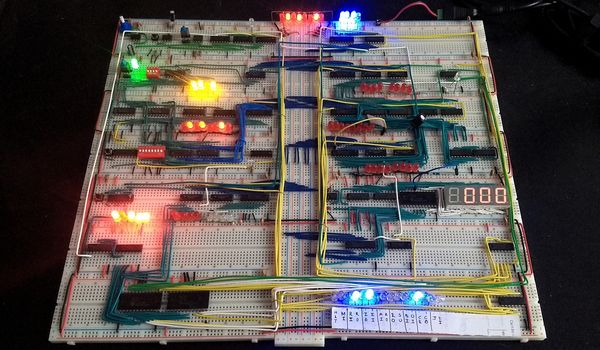

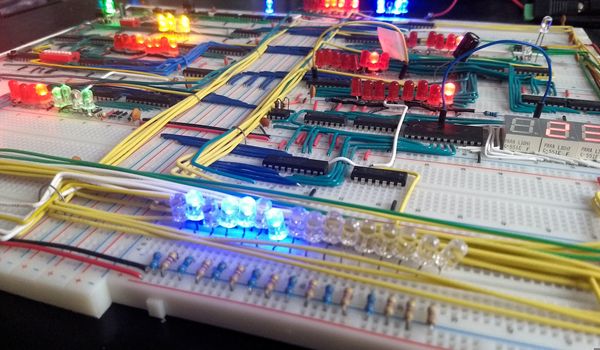

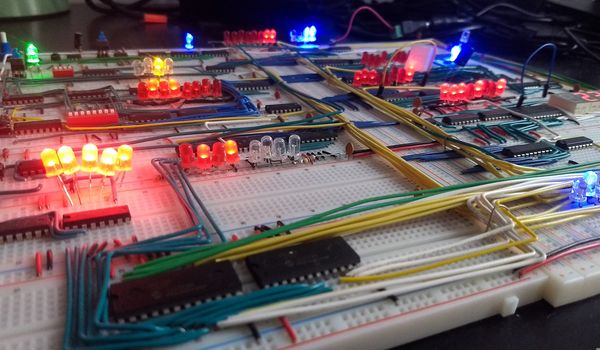

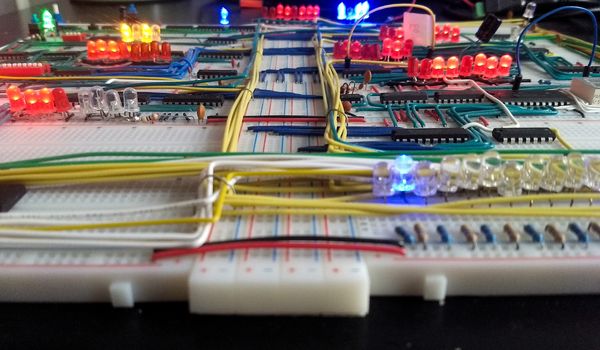

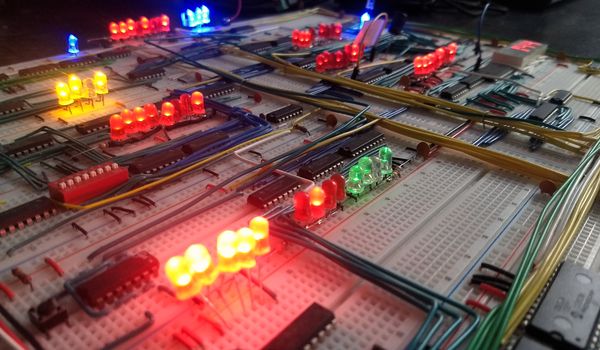

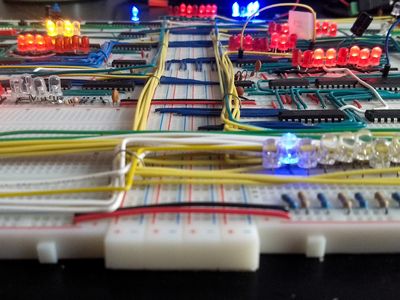

Vários anos depois, encontrei por acaso a CPU de 8 bits em protoboards do Ben eater. Nessa série de videos, Ben Eater segue um caminho parecido com o do livrop, e monta um computador funcional a partir de circuitos integrados da série 7400.

É óbvio que eu decidi montar um.

Em resumo, eu simplesmente segui os videos e diagramas de circuito publicados por Ben Eater.

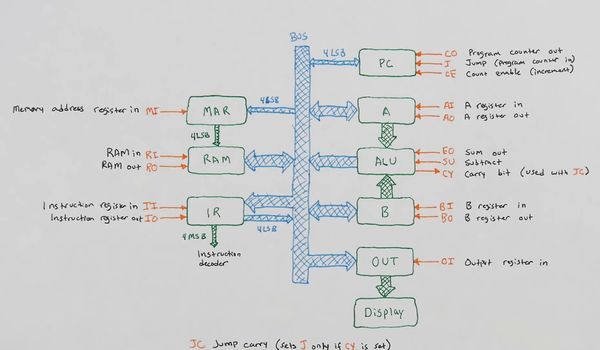

A estrutura básica do computador é a seguinte:

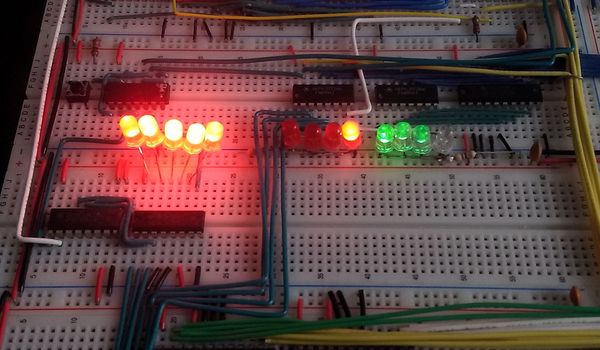

É, claro, um computador muito simples. Na verdade, aparentemente ele é baseado no SAP-1 descrito por Albert Paul Malvino no livro Digital Computer Electronics. Na implementação do Ben Eater (e na minha), o conjunto de instruções é muito pequeno. Só existem instruções para manipular dados em um dos registradores e só existem dois pulos condicionais: pula se vai um e pula se zero.

NOP 0000

LDA 0001

ADD 0010

SUB 0011

STA 0100

LDI 0101

JMP 0110

JC 0111

JZ 1000

OUT 1110

HLT 1111

O design usa EEPROMs para substituir a lógica combinatória necessária para decodificar as instruções e disparar os sinais necessários para executá-las. O opcode e o contador de ciclo de instruções são usados para endereçar a EEPROM e as saídas (ou seja: os dados no endereço correspondente) são os sinais de controle. Isso significa que é possível atualizar o microcódigo do computador reprogramando essas EEPROMs.

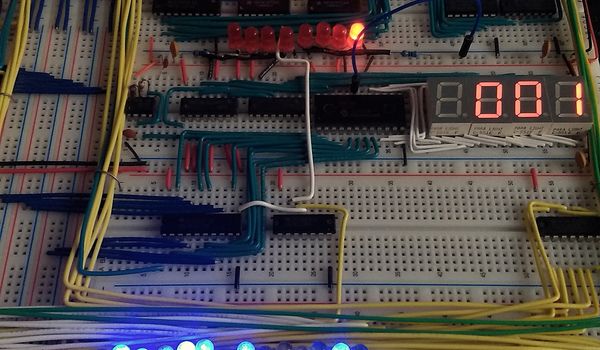

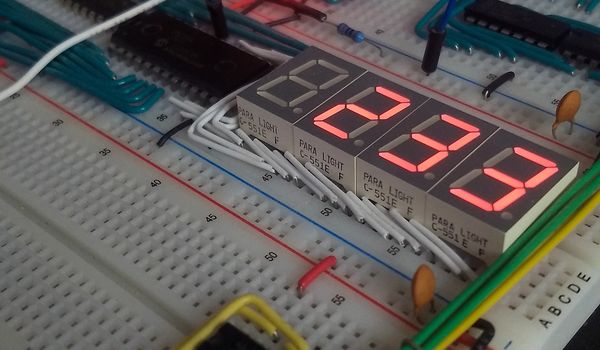

Com só 4 bits para o endereçamento de memória, precisamos colocar todo o programa e os dados em 16 bytes. Um simples programa pra calcular a sequência de Fibonacci usa quase toda a memória:

| Opcode | arg | pos. de mem | conteúdo |

+--------+-------+----------------+--------------+

LDI 1 0000 0101 0001

STA 14 0001 0100 1110

LDI 0 0010 0101 0000

ADD 14 0011 0010 1110

STA 15 0100 0100 1111

LDA 14 0101 0001 1110

STA 13 0110 0100 1101

LDA 15 0111 0001 1111

STA 14 1000 0100 1110

LDA 13 1001 0001 1101

OUT 1010 1110 0000

JC 0 1011 0111 0000

JMP 3 1100 0110 0011

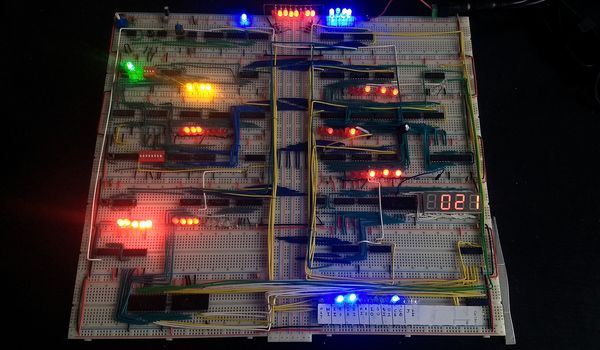

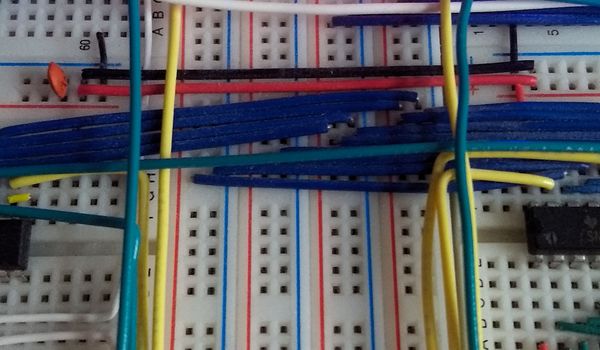

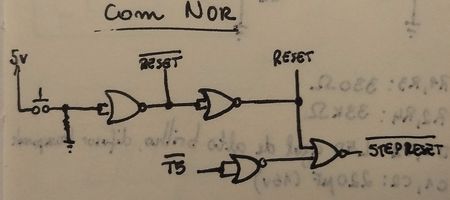

Um detalhe em que meu circuito diverge do do Ben Eater é no circuit de reset. Eu não tinha portas NAND à mão quando queria montar o circuito, mas tinha postas NOR. Eu, então, adaptei a lógica de reset dele para usar portas NOR.

Um outro problema que eu encontrei é que às vezes a memória RAM era

sobrescrita quando eu

trocava entre o modo de execução e o modo de programação. A

solução é colocar um

resistor de pull up no pino write enable do CI de RAM pra que ele

não fique indefinido quando o botão não está sendo pressionado.

Existe um subreddit dedicado ao canal do Ben Eater onde várias pessoas postam programas diferentes e modificações de hardware. Algumas pessoas fizeram programadores, expandiram a memória etc. É uma boa fonte de informações sobre o projeto e um bom lugar pra procurar soluções pra eventuais problemas.